Chapter Updates and Reaching CID+ Certification

This month’s column will detail the proceedings from the most recent IPC Designers Council (DC) Executive Board meeting. You will find updates on local chapters – from the United States (spotlight on the Silicon Valley chapter) to Mexico, France and Asia – educational opportunities, upcoming events, and one engineer’s story to achieving CID+ certification.

Attendees

The IPC DC Executive Board meeting included local members and leaders and a variety of IPC course instructors representing chapters across the United States: Tony Cosentino, Randy Faucette, Mike Creeden (MIT), Scott McCurdy, Bob Griffith, Gary Ferrari (MIT) Rick Hartley, Bob McCreight, Susy Webb, Paul Fleming (CIT), Faisal Ahmed, and myself (Stephen Chavez).

Global Steering Committee

The global steering committee meetings were approved at the last IPC DC Executive Board meeting and formally began at the most recent meeting. The next meetings are scheduled for IPC Apex Expo 2019, the third week in May, and PCB West in September. As mentioned in my last column, I was nominated and approved to chair a new communications committee comprised of representatives from each of the IPC DC chapters. The first order of business was to resurrect the council’s newsletter with industry media companies to discuss chapter reports, events, and other related news.

Chapter Spotlight

by Bob McCreight, Silicon Valley Chapter president

The IPC Designers Council is an international network of designers. Its mission is to promote printed circuit board design as a profession and to encourage, facilitate, and promote the exchange of information and integration of new design concepts through communications, seminars, workshops, and professional certification through a network of local chapters. This month’s spotlight is the Silicon Valley Chapter. We held our fall quarterly meeting on October 25 at none other than Levi’s Stadium in Santa Clara – yes, the site of Super Bowl 50 and the soon-to-be 2019 College Football Playoff National Championship game. This was made possible by our host, Sierra Circuits, and sponsor, Altium. We thank them both graciously. Out of 33 total RSVPs, 24 were able to attend the lunchtime meeting. Fun fact: of the members who RSVPed, six of them were CID certified and 10 were CID+ certified with Faisal Ahmed being the most recent (hear more from him later).

Amit Bahl

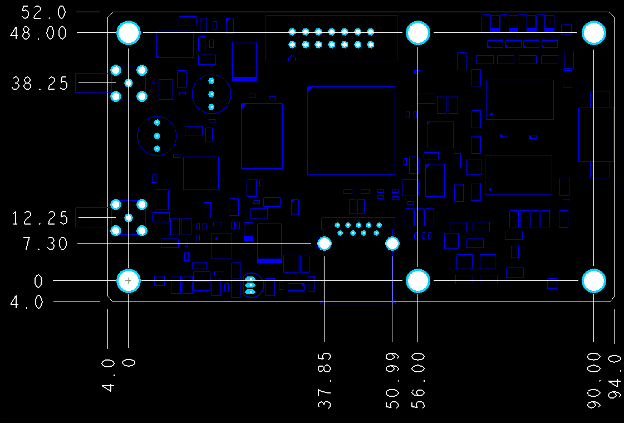

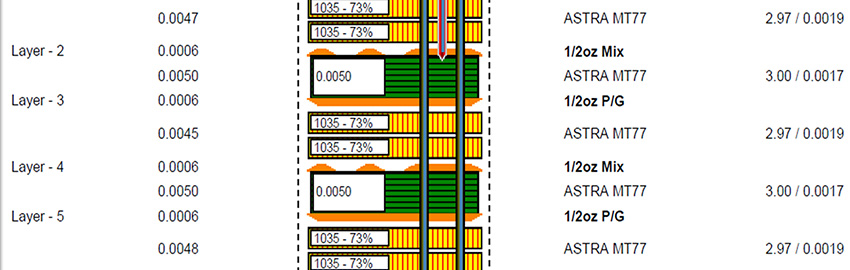

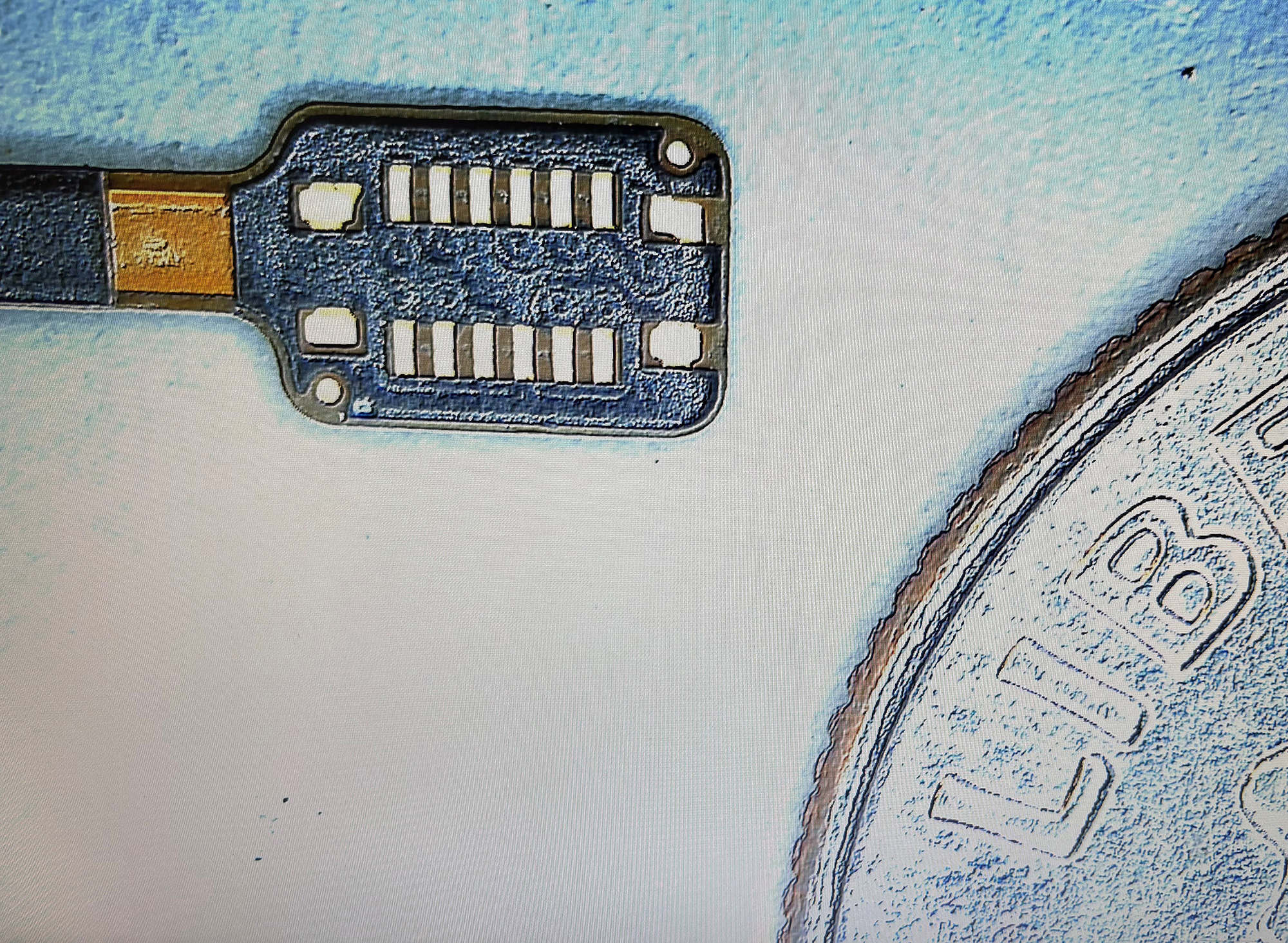

After addressing some chapter business, Amit Bahl, director of sales and marketing at Sierra Circuits, spoke about a newly patented process called CATLAM. Watch for a new term they are coining – trench circuit board (TCB). The secret sauce they are developing involves etching a trench in the PCB material and filling it with copper by an electroless process, for which there are numerous benefits.

Ben Jordan

Following that, we introduced Ben Jordan, director of community tools and content at Altium. He gave us a brief preview of Altium Designer 19. Not to give away too much right now, but library management has some really cool new features, some of which will leverage their Octopart extension.

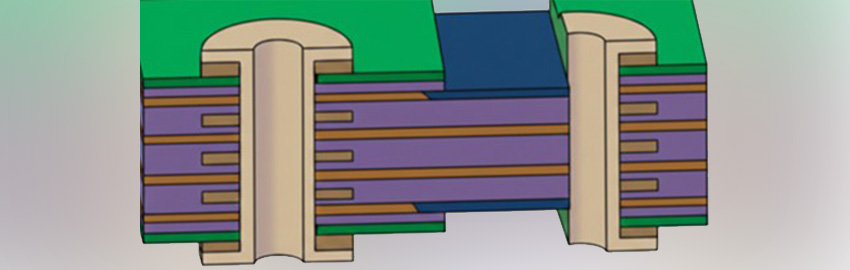

For the main presentation, Ben gave an overview of multi-board design, which involves projects that have more than one PCB and are interconnected by either plug-in connectors, wire harnesses, or another method. Some of the examples Ben demonstrated were very cool, like his own guitar mixer box. One point that he stressed was to put plenty of thought into how you divide the boards up. For instance, the power supply can be on a simple two-sided board while the communications can be on a more complex multilayer board. Mixing them may have signal integrity consequences.

Following the conclusion of the meeting, the networking portion of the agenda was blended into a stadium tour. From our seventh-floor boardroom, we went up the elevator to the NRG Solar Terrace, or “Green Roof,” where there is a thriving, sustainable garden that basks in the brilliant sunlight. From part of the terrace, you get a grand view of the field plus Silicon Valley and the southern San Francisco Bay Area, which you can also rent for events. Next, we visited the Verizon Press Level where all the media hangs out during game day action. We ended by visiting the field itself, including being able to look up at all the seating, lighting, and signage. It’s a very nice stadium if I do say so myself. Too bad the home team is not doing so well this year (sad face).

Figure 1 Levi’s Stadium field tour.

Below is our tentative 2019 meeting schedule (exact dates may vary):

- January 24, sponsored by Mentor

- April 25, sponsored by Cadence Design Systems

- July 25, sponsored by Altium

- October 24, sponsored by Zuken

We are looking for great speakers so feel free to volunteer! Last, I’d like to extend many thanks to those who attended, Ben Jordan and Judy Warner from Altium, and Amit Bahl and his team at Sierra Circuits, including Lucy, Rachel, Bianca, and Joel.

Why CID+?

by Faisal Ahmed, Cadence Design Systems

A recent Silicon Valley Chapter member – Faisal Ahmed, lead application engineer at Cadence Design Systems – recently took an IPC CID+ course at PCB West 2018. He shares why he pursued IPC advanced designer certification, and his thoughts on successfully achieving CID+ status.

After 20 years of creating masterpieces of art with copper on glass resin, I decided to take on advanced designer certification (CID+). Many of my friends in the industry have asked, “Why so late and what did I achieve?” To answer that, being CID+ gives me the highest possible PCB design status in the industry.

One recent survey found that two-thirds of PCB designers are 51 to 70 years of age; astoundingly, one-fourth are 41 to 51, which leaves me in the youngest 10% of designers. To my friends out there, I am not late, but don’t worry if you fall in the top 90%. As George Eliot said, “It’s never too late.” It is to your advantage to get the certification when you really know the industry and are proficient with the PCB design flow. Unlike CID certification, which is designed for anyone at any level involved in developing, designing, fabricating, and producing PCBs – from sales to management, procurement, and quality – CID+ certification is designed for the advancement of the designer.

The process of reviewing PCB design from new product introduction (NPI) to the end product with the fear of being tested on the content helped me focus on the material and provided me with an enhanced learning experience. In product development, PCB designers are the liaison who converts electronic ideas into reality; therefore, it is critical for them to understand electronics and manufacturing.

Being an IPC Advanced Certified Interconnect Designer or CID+ is the ultimate certification for a designer, and it certifies me to be an industry professional.

Chapter Updates

San Diego, California: Bob Griffith

• Status: Strong

• Regular attendees: 70–75

• Meetings per year: Five (four core meetings) during lunch

• Leaders: Six core executive chapter members

• Events: Host city to IPC Apex Expo 2019

Orange County, California: Scott McCurdy

• Status: Strong

• Regular attendees: 45–70

• Meetings: Four during lunch

• Leaders: Four core executive chapter members

• Successes: Lunch meetings and diverse speakers

Silicon Valley, California: Bob McCreight

• Status: Active

• Regular attendees: 20–30

• Meetings per year: Four during lunch

Seattle, Washington (Cascade Chapter): Tim Mullin

• Status: Active

• Regular attendees: 8–14

• Meetings per year: Four during lunch

• Leaders: Five core executive chapter members

• Successes: New members being brought in through local CID/CID+ training; hopefully, this will continue with the formation of a new Altium user group following chapter meetings

• cascade-ipcdc.org

Phoenix, Arizona: Stephen Chavez and Paul Fleming

• Status: Dormant

• Leaders: Four core executive chapter members (seeking new leadership to take over)

• Meetings per year: None currently (but typically, four)

Research Triangle Park (RTP), North Carolina: Tony Cosentino and Randy Faucette

• Status: Strong

• Regular attendees: 30

• Meetings per year: Three to four during the evening

• Leaders: Nine core executive chapter members

• Events: Annual PCB Carolina event with 700–1,000 attendees

Monterrey, Mexico: Luis Saracho

• Status: Active

• Regular attendees: 8–12

• Meetings per year: Four during the evening with technical presentations

• sites.google.com/view/mtyipcdc/home

Design Council Chapter France (DCCF): Thomas Romont

• Status: Active

• Regular attendees: 34–60

• Successes: Professional presentations and workshops, design community surveys

• Events: February 2018 was the first DCCF conference in Paris (IPC Day Design)

Penang, Singapore, and Philippines Chapters: Cheah Soo Lan

• Status: Active

• Regular Attendance: 73 (Penang), 30 (Singapore), 14 (Philippines)

• Successes: CID and CID+ certifications

• Events: Plant visits (Singapore)

Education

New IPC Edge 2.0 Program

• Mandatory testing

• Required 80% to pass

• Must score 16 out of 20 or higher

• Must take the same test for each IPC certification

Upcoming Activities at a Glance

Two-day hands-on power integrity workshop: Steve Sandler

• December 3–4, 2018

• Santa Clara, California

• Registration: landing.protoexpress.com/powerintegrityworkshop

• Contact Lucy Iantosca at Sierra Circuits for details

IPC Apex Expo 2019

• January 26–31: Meetings and courses

• January 29–31: Conference and exhibition

• January 31–February 2: IPC Designer Certification CID/CID+

• San Diego, California

• ipcapexexpo.org

DesignCon 2019

• January 29–31

• Santa Clara, California

• designcon.com

Next month will cover the upcoming IPC Apex Expo in late January and highlight the San Diego Chapter.

Stephen Chavez is a member of the IPC Designers Council Executive Board and chairman of the communications subcommittee. To read past columns or contact Chavez, click here.