Draw the map and make it happen.

Draw the map and make it happen.

As the saying goes, Rome wasn’t built in a day.

That doesn’t refer to the city-state as we know it, but rather the empire as it was back in the day for my hometown of Augsburg, Germany. Located where the Wertach River joins the Letch River on its way to the Danube, which flows from the Black Forest to the Black Sea. The Danube is a long river starting in Germany and ending at the border between Romania and Ukraine.

You might be wondering what all of this has to do with placing components on a PCB.

The global circulation of water is a little like the distribution of power on the board. There is a source and an endpoint, but it’s a closed system. Tributaries may diverge or converge to provide access to cities and towns along the way. Those features are formed naturally by erosion. Similarly, we etch away the copper on a PCB using chemistry. The steering effect is the same in the end.

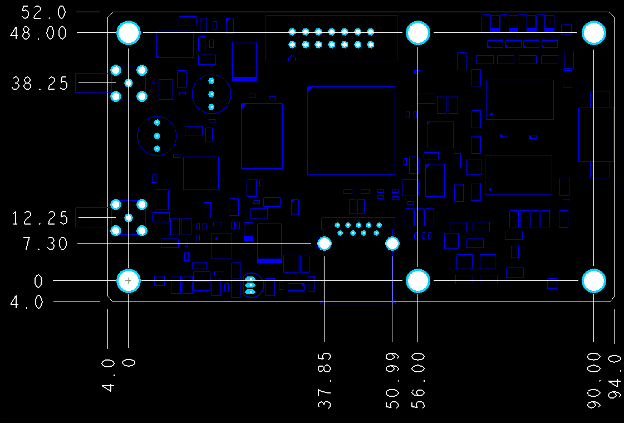

This is what I picture when looking at a board outline and a cluster of components arrayed on the outside, as in Figure 1, for instance. A connector on the board carries the current that drives all the various devices along a path the designer provides. In place of the four capital cities that populate the banks of the Danube, think of the processor, memory, WiFi and sensor(s) as towns linked by a flow of invisible energy.

Figure 1. This disk drive shows how the four larger power pins are segregated from the signal pins using one application-specific connector. (Source: Author)

There is a whole different set of cases on the other side of the globe where a single ocean is the main feature. A quick aside: the Hawaiian people have two words to describe directions that make more sense than north, south, east and west. Makua refers to “toward the mountain,” while makai points us to the sea. The chip is the mountain, and every pin must get down to the beach to float away on the current (Figure 2).

Figure 2. The idea that everything flows to the sea is central to a good fan-out strategy. The nucleus of an atom is another good metaphor for the influence of a device on all the dependent components. (Thought you might like a pause on the windward coast.) (Source: Author)

Power: Where the PCB drama lives. Making power connections is a world unto itself. Power integrity has surpassed signal integrity in terms of the amount of detail to consider. It’s assumed that the design will deliver on all the point-to-point routing involving the traces. You isolate the victims, especially from the aggressors. Since space is at a premium, it is a balancing act. Most islands don’t have wide roads.

It’s up to you to know when to use shepherd vias to maintain the sanctuary around the differential pairs and bus lanes. I’ll pour the copper and go from there to “massage” the circuit layout to get those ground vias around the bus. Resolving timing budgets is assumed. These are the table stakes for the PCB designer in today’s world.

This is for certain: Traces will be routed and then altered. That part was much harder when I started in this business. Now, we can be gentle with an existing trace. If we like it, we can hug it. If we need to make way for improvement, we can shove the existing trace out of the way.

Don’t get me started on the dynamic copper that politely steps aside when you come routing through with a new connection. CAD tools have grown along with the complexity of the boards. There’s no going back, so familiarity with the latest features of the tools is useful. The shape-to-shape air gap constraint can be a safety requirement, particularly for higher voltage.

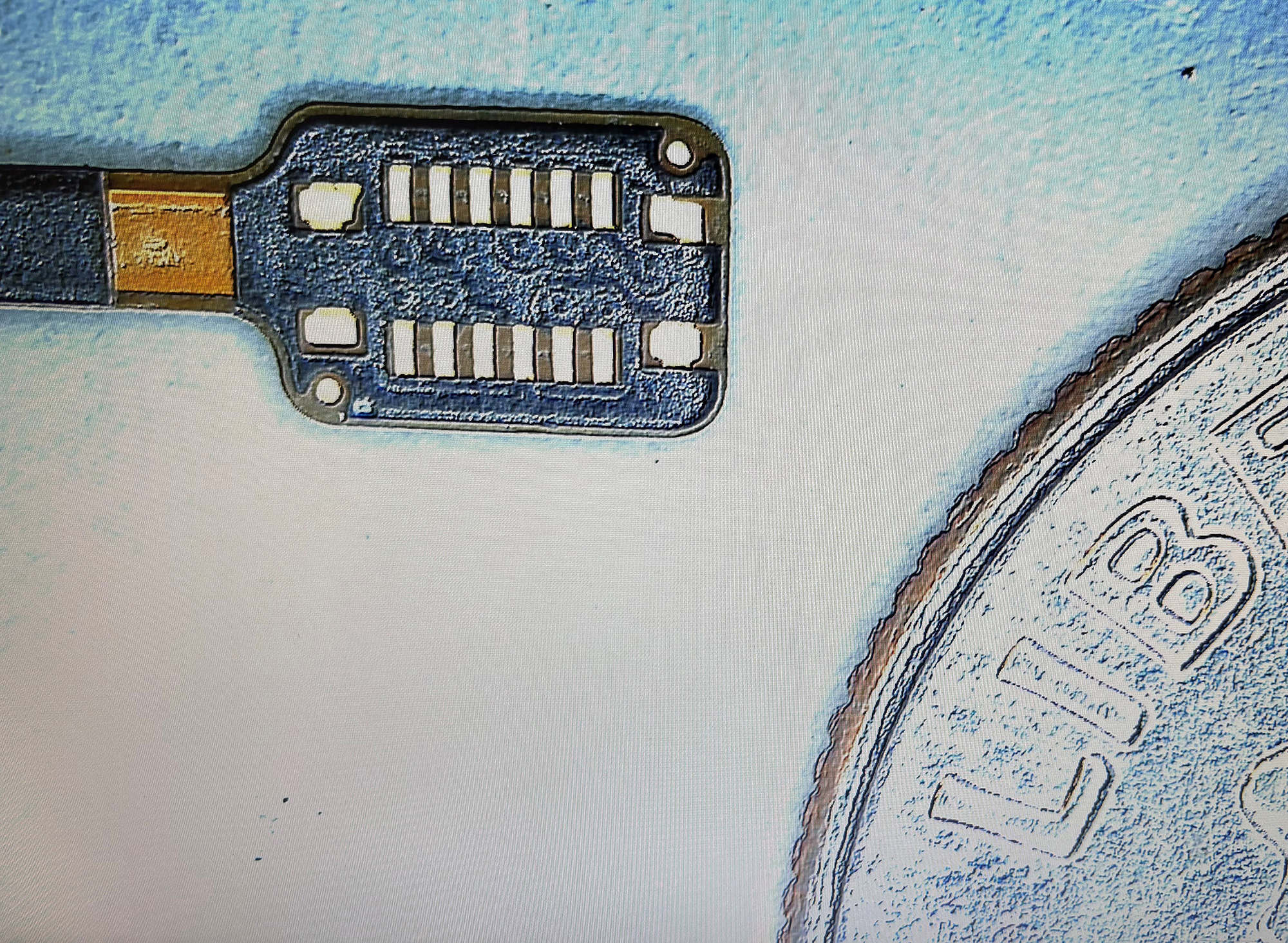

Figure 3. A Qualcomm PMIC with 12 switch-mode power supplies in one package. It appears that the caps are placed before the inductors, although the inductors are the main part of the noise suppression. The series L wants to be first, while the shunt caps can fit there, so you do what you can with what you have. (Source: eBay)

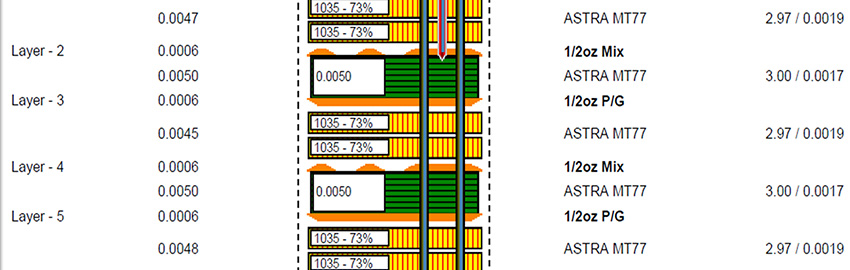

Power management ICs: An SoC’s best friend. This is the routing strategy difference between microvias and through-hole vias. The farther into the rings of BGA pins you go, the deeper the vias have to reach in the z-axis to find a path away from the core of the device. The devices receive power from different voltages, and those voltages separate further by function. Numerous regulators are in play, some dialed into the same voltage, such as +3.3VDC. The same 3.3V domain won’t be used for all the 3.3V pins. There’s often a need for 2.5V, 1.8V and so on, including negative voltages. Splitting it is usually the job of a power management IC, or PMIC, which is a collection of regulators in one package. (More than one package may be needed to feed a SoC.)

Those who have used a switch-mode power supply know they depend on a sizable inductor that is often larger than the individual device. Those inductors more or less surround a PMIC. The inductors and obligatory capacitors make a pair that is always too big to situate adjacent to the output pins, which are always on the outer row of the BGA package.

Instead, they must be moved from the PMIC, forming a row which we connect to the output pins using fan shapes that radiate outward, getting thicker as they approach the inductors. We want them closer for noise abatement, but that’s physically impossible. PMICs are a compromise every time.

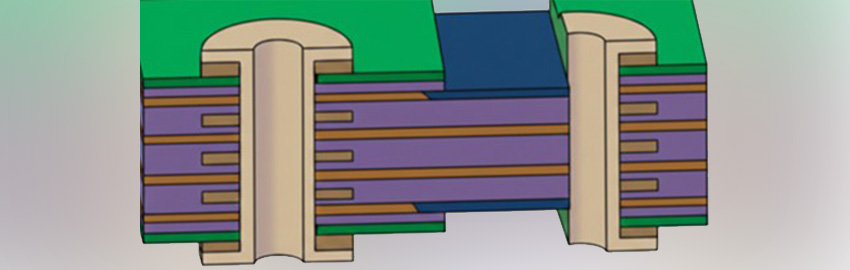

Figure 4. Power and control are on display. This PCBA is charged with rotating a LiDAR sensor 20 times per second while also powering up 32 lasers and 32 detectors for simultaneous location and mapping (SLAM) functionality. Robots, cars and mining equipment are all candidates for electronic spatial awareness. (Source: Author)

I write that power is king because so many things run on battery power, where efficiency is the key factor. It isn’t just mobile devices, though. No electronic product wants to hog power. We want to be greener, of course. Doing a bang-up job on the power delivery network (PDN) and executing on the high-priority traces is the green solution all along.

More integration equals greater power demand. The higher integration on today’s devices is one of the daunting challenges in PCB design. The processors of that bygone era had a pin-count in the upper four hundreds with a single core to feed. The spacing of the pins was more generous at 2.5mm down to 1mm, or perhaps 0.8mm at worst. We can only dream of working with that much space between pins.

Now, we’re dealing with devices with half of that pitch. The struggle with 0.4mm pitch BGAs is real. An IC can still be an island, but now the SoC is doing so many different things, it looks more like a metropolis. A hierarchy of devices will be close to the SoC. Dynamic and static memory devices are first and second in line.

The remainder of the various parts must hope for a location “good enough” to do their thing. Generally, the power domains dominate the decisions. Then there are cases like USB connectors or antenna locations where the components are crowded into a specific part of the board. Those are the outlying islands where contact is limited, maybe even discouraged.

Thermal considerations drive PDN decisions. Big power means big heat. Laying down a grid of power pins will not be effective without a similar number of vias associated with the ground domain. The ground patch can be the answer, but may also be augmented with a heatsink. The heatsink can be directly attached to the hot spot or a heat pipe can be used to transfer energy to an outboard heatsink. These are your rivers and reservoirs that carry away and contain the thermal exhaust of our hard-working chipsets.

Placement can be quite European with small domains clustered together. Still, each part of the power grid likes to be isolated from the others. The bridges and tunnels of New York provide a colorful map of all the boroughs with minimal interconnects. I tend to see each board as some kind of geography, whether a metropolis or a charming village. Those simulation games always need room for the utility companies, and likewise, the boards want their specific power structures. Draw the map and make it happen.

John Burkhert, Jr. is a principle PCB designer in retirement. For the past several years, he has been sharing what he has learned for the sake of helping fresh and ambitious PCB designers. The knowledge is passed along through stories and lessons learned from three decades of design, including the most basic one-layer board up to the high-reliability rigid-flex HDI designs for aerospace and military applications. His well-earned free time is spent on a bike, or with a mic doing a karaoke jam.

Draw the map and make it happen.

Draw the map and make it happen.