The latest reports from the local chapters.

The latest reports from the local chapters.

This month’s column highlights the Monterrey Designers Council Chapter located in Monterrey, Mexico. The chapter was established Nov. 23, 2017, which makes it a younger chapter compared to several other global chapters currently in existence. I also share news about a new chapter forming in Nogales, Mexico.

Luis Saracho is president of the Monterrey Chapter and an IPC Certified Advanced PCB Designer (CID+) with a true passion for designing board layouts, not to mention leading and organizing chapter meetings. This chapter has yet to establish a solid leadership team, so Luis is basically running the show on his own and has been doing an awesome job keeping this chapter active and successful. The chapter meets quarterly, with an average attendance of 12 to 18 attendees. Chapter meetings are typically held in the evening at a local university (ITESM Campus Monterrey), and most meetings consist of a technical presentation. The chapter is looking into getting government support through CANIETI – an organization that supports technical initiatives – but has had poor results to date.

Chapter Spotlight: Monterrey

by Luis Saracho, CID+, Chapter President

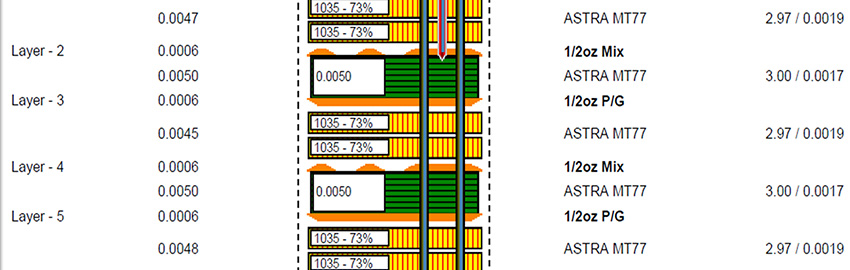

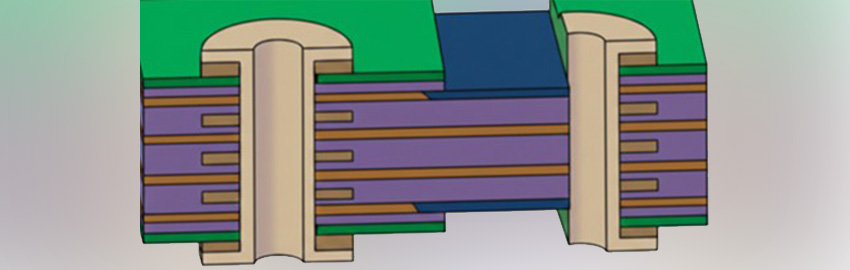

Our recent chapter meeting, held May 30, went well overall. There were 20 to 25 attendees from different workplaces, with several industry fields represented, including automotive, industrial, lighting, manufacturing of electrical households, etc. Attendees shared their experiences with analog/digital/power grounding techniques on printed circuit boards (FIGURE 1). Areas of conversation included:

- Keeping only one ground plane

- Splitting planes but keeping them connected at a single point

- Pouring with ground the signal layer as ground guards

- Keeping separated ground potentials.

Figure 1. Technical discussion on power grounding.

At the end of the meeting, the conclusion from the open technical discussion was no recipe fits for all the diverse products people work on. Design rules and considerations for a graphics controller, 10-layer, mid-power board cannot be followed for a double-layer, high-power board design for industrial applications.

The only recommendations agreed on by everyone were to keep the loop between power and its return as small as the layout permits and avoid crossing loops, referring to a wide range of design options. But considering the diverse audience, it was interesting to hear where they had design flaws on EMC/EMI and what engineers did to correct those flaws. The same specific rules cannot be applied to designs for different applications and technology. The magic relies on identifying the aggressive and sensitive loops, and if simulation or testing shows a flaw, understanding the root cause. This is not an easy task for printed board engineers.

If you want to contact me, email This email address is being protected from spambots. You need JavaScript enabled to view it.. Learn more about their chapter at https://sites.google.com/view/mtyipcdc/home.

Luis Saracho, CID+, Chapter President

A New Designers Council Chapter

The Monterrey DC Chapter will no longer be the only chapter in Mexico. In a recent IPC CID certification class I taught at the Chamberlain Group located in Nogales, Mexico, the spirit of comradery, success and knowledge sharing was truly overwhelming, so much so that the entire group made up of EEs wanted more than one would typically get from a four-day IPC CID certification class. They wanted to get “involved” and become part of the industry IPC collective, especially regarding PCBs/CCAs. They also wanted to represent their country in the best possible way as the next wave of EEs.

The group is led by Heriberto (Heri) Alanis, an extremely knowledgeable EE and industry veteran with over 30 years of experience. Heri is also an excellent mentor for many of the young engineers within Chamberlain Group. He will have a strong support network to establish this new chapter. His core members, who will form the leadership of this new chapter and are all recent achievers of their IPC CID certification, are as follows:

- Rodrigo Martin del Campo Alcocer

- Roberto Ivan Villalba Gonzalez

- Jacob Ivan Castellanos Juarez

- Carlos Arturo Garcia Gamez

- Rafael Antonio Gomez Sandoval

- Marcos Eduardo Chavez Manon.

This new chapter from Nogales, Mexico, will be the spotlight for next month’s column as they establish their presence in the global IPC Designers Council community of other local chapters.

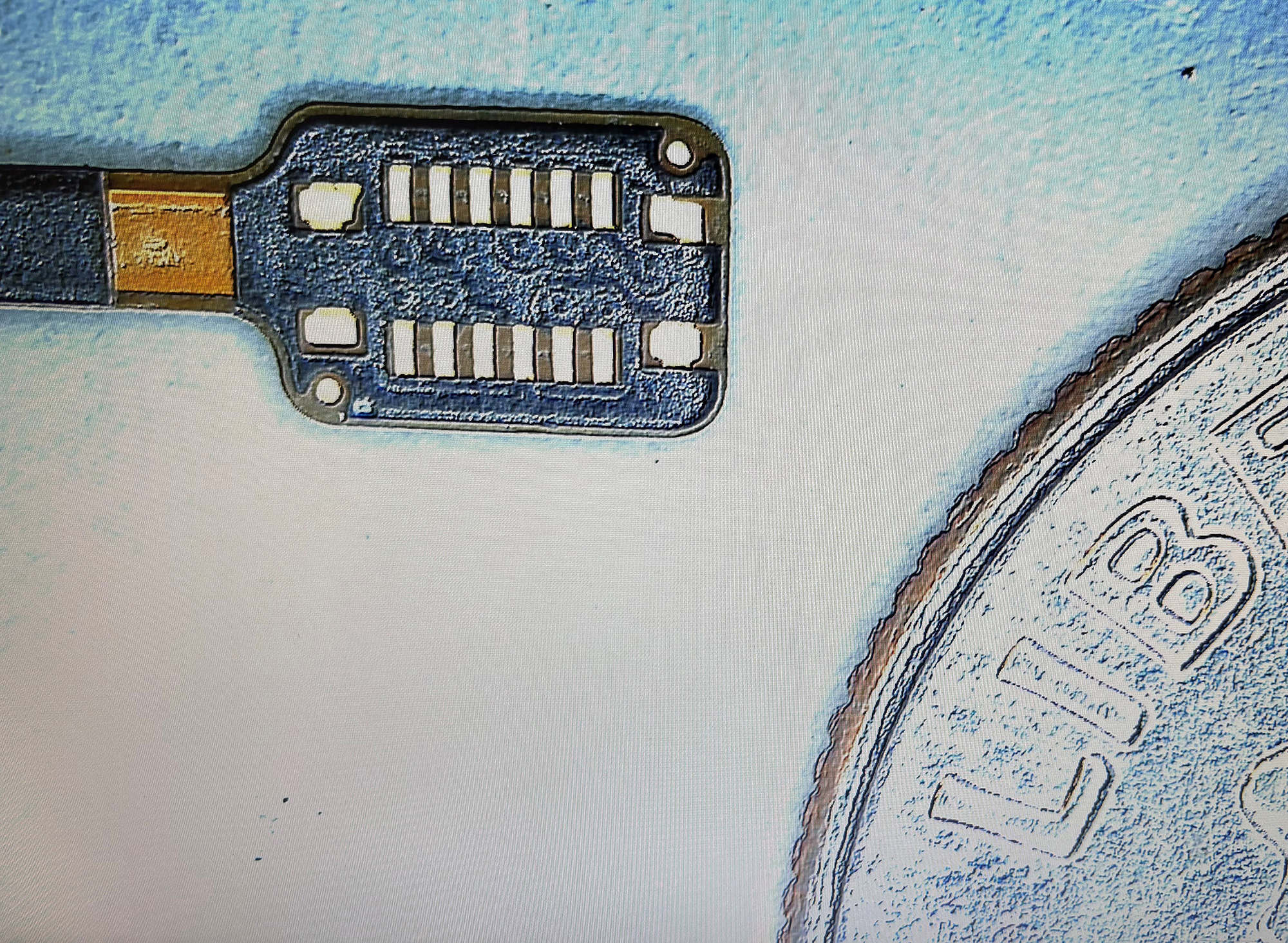

Figure 2. May 2019 Monterrey Chapter meeting.

2019 Training and Certification Schedule

IPC Certified Interconnect Designer (CID)

August 6–9: Baltimore, MD

August 26–29: Markham, ON

September 6–9: Santa Clara, CA

September 19–22: Schaumburg, IL

October 8-11: Carmel, IN

October 21–24: Anaheim, CA

November 2–5: Raleigh, NC

November 5–8: Dallas, TX

IPC Advanced Certified Interconnect Designer CID+

September 6–9: Santa Clara, CA

September 10–13: Kirkland, WA

September 17–20: Schaumburg, IL

October 21–24: Anaheim, CA

November 2–5: Raleigh, NC

December 3–6: Manchester, NH

Note: Dates and locations are subject to change. Contact EPTAC Corp. to check current dates and availability. A minimum enrollment of seven students is required for a class to be held.

PCB Design Events

PCB West 2019

September 9–11: Santa Clara, CA

pcbwest.com

AltiumLive 2019

October 9–11: San Diego, CA

altium.com/live-conference

Stephen (Steph) Chavez is a member of the IPC Designers Council Executive Board and chairman of the communications subcommittee; This email address is being protected from spambots. You need JavaScript enabled to view it..