BILLERICA, MA – Cadence Design Systems today rolled out a major revision to its Allegro and OrCAD platforms, adding a host of co-design functionality to the high-end suite while also moving certain sophisticated PCB design features to its OrCAD platform. The EDA design software company also reconfigured the suites to a core format with several add-on modules that users can license on-demand, thus reducing the cost of licensing a full suite of tools.

In an interview with PCD&F today, group director, product marketing Keith Felton explained the rollout would ease pressure on customers who want only to use – and pay for – certain elements of the suite. He also noted the emerging delineation between Allegro and its mainstream cousin, OrCAD.

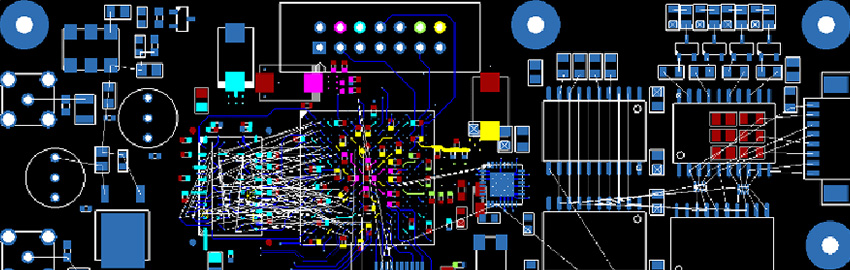

OrCAD v. 16.5, which remains a major source of revenue for Cadence, has been reconfigured into three offerings: Professional, Standard and Lite. The company also beefed up the OrCAD suite, moving some of the Allegro functions to OrCAD, which now contains everything from schematic entry to signal integrity and high-level autorouting, and CIS functionality (see table, below).

"If you look at the mainstream market, customers are more cost conscious and want more capability,” Felton said. “We’ve taken a ton of Allegro capability and disconnected it so it’s only available at the OrCAD level. And the pricing on OrCAD has actually gone down. We’ve increased the capability and reduced the pricing.”

Allegro v. 16.5 features several updates to the core system-in-package and power design network tools. SiP, Cadence learned, wasn’t embraced by fabless semiconductor companies with design teams spread around the world who were concerned about IP security. “We were parsing chip IP in the form of Open Access databases, and chip designers didn’t want to do that. We’ve now moved to distributed codesign where teams can parse abstracts of the chip, like pinouts. It’s an .xml version of the chip that contains the physical descriptions but not the chip IP. We do that for digital chips, custom analog chips, and mixed signal.”

The new PDN solution, a full-wave field solver technology developed collaboratively with the University of Illinois, features algorithms that prove and validate a user’s power network analysis.

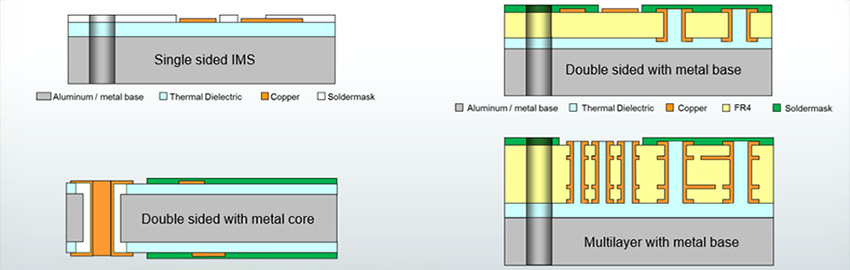

The “Miniaturization” module enables embedding components using constraint-driven place and route techniques.

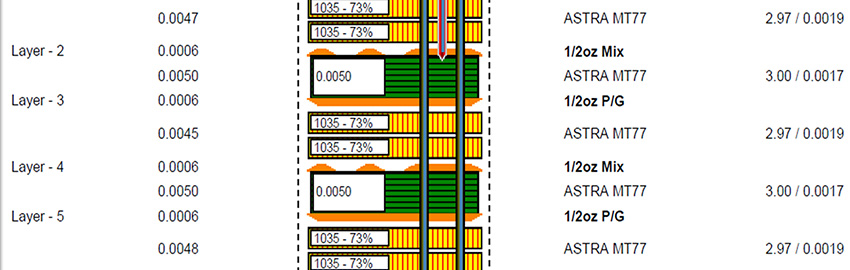

The new PCB interconnect design planning technology shortens time to route dense, highly constrained boards, Felton said. Here, Cadence adopted some of its Allegro GXL suite’s design configuration for the base product. They also created a new feature driven by constraints and timing.

Allegro v. 16.5 also offers support for OEM/ODM joint development model using distributed libraries to protect IP. “We’ve come up with a way for ODMs and OEMs to share partially distributed libraries while masking out info they don’t want to disclose, and while also tracking that shared library so they can tell if it’s been edited,” explains Felton. “It addresses one of the key issues joint development teams have to overcome.”

Finally, OrCAD and Allegro continue use the same database, making it easy for designers to move up without requiring translations.

Perhaps the biggest change is the shift to a hierarchical model in which Allegro is offered as a highly functional base model with several add-on components for analog, RF, team design, routing and other technical features.

Most Allegro products are used by large enterprise customers, Felton said, yet even so many of them do not fully exploit the suite’s full capability. Under the new “base-plus” model, users can invoke options for team design, miniaturization, and so on as needed. “A lot of customers only wanted a specific piece and couldn’t justify buying the whole configuration. Because we’ve broken the function down into modules, they can better manage the licenses in the company and better justify their purchases,” Felton said. Each option can be used independently as well, he added. “It’s the lightest-weight option to get your job done.”

The modules can be run on top of the base configuration. Each option has an individual floating license. Customers can manage which engineers can access the licenses, as desired. Cadence continues to support perpetual and time-based (one to three year) licenses, and peak usage purchases (“EDA cards”), which allow users access to modules for periods as short a week.

Customers clearly will be eager to see how the change in the license model might impact maintenance. While Cadence will no longer sell the old configuration, existing customers can migrate to the new model only as they want to; they won’t be forced to switch, Felton said. “We think this will actually stimulate some growth in the tool use.”

Felton believes disconnecting the modules from one another could speed the pace of updates and would them to take place without affecting other tools.

On the surface, Cadence appears to be grouping the full suite of its PCB tools in OrCAD, meaning the designer who needs only to focus on bare boards and not on chips has plenty of room inside that suite to operate. Meanwhile, all chip-level and higher level co-design tools are available in Allegro.

"We’ve never had a release so significant in terms of new feature content and restructuring of the price book," Felton said. “We hope customers will see this as a recommitment to the PCB market both in technical sense and in that the new configuration brings more product capability to each engineer's desktop.”

Table 1. OrCAD 16.5's Offerings

|

Professional

|

Standard

|

Lite

|

|

Schematic Entry

|

X

|

X

|

Limited

|

|

OrCAD PCB

|

X

|

X

|

Limited

|

|

L-level PCB features

|

X

|

|

Limited

|

|

Performance-level features

|

X

|

|

Limited

|

|

Signal Integrity

|

X

|

|

|

|

Autorouting

|

X

|

|

Limited

|

|

256-layer autorouting

|

option

|

|

Limited

|

|

CIS

|

option

|

option

|

Limited

|

|

PSpice A/D

|

|

|

Limited

|

|

PSpice A/A

|

|

|

Limited

|

Ed.: The original version of this story contained the following errors: embedded component support was listed as part of OrCAD; it is actually part of the new Miniaturization option of Allegro. Also, Design Planning technology has been extracted from Allegro GXL, not Virtuoso GXL. PCD&F regrets the errors.