Gone are the days when designers had to jury-rig layout tools to do RF designs. Now, even virtual RF prototypes are simple, if you know a few tricks.

RF and microwave PCB design is becoming evermore complex, driven largely by the need for higher levels of circuit integration. It is not unusual to find analog and digital circuitry coexisting on the PCB together with traditional RF/microwave circuitry. This presents a number of significant challenges, not least of which is the design flow methodology. Often, designers use a number of disparate CAD tools during the development phase of complex RF PCBs. This can introduce unforeseen problems into the design during integration, particularly during the PCB layout.

We will demonstrate how electromagnetic simulation techniques can be used to extract the high-frequency PCB layout parasitics and enable creation and simulation of a virtual, or software-based, RF PCB prototype prior to fabrication. We describe a real-world case study where this methodology was successfully used to detect and remedy unexpected problems caused by layout parasitics on a reference design for a satellite TV tuner.

In an ideal world, a PCB design would be developed in a unified EDA/CAD environment with all of the necessary capabilities to allow designers from different disciplines - RF/microwave, analog, digital, signal integrity, layout, mechanical, etc. Designers would be able to develop a design efficiently, verify the design performance against the requirements specification and generate a detailed data pack to support the manufacturing process. The resulting first-pass design would both accelerate time-to-market and remove the expense associated with design re-spins, both of which are important factors if the design is to be a commercial success. Unfortunately, this Utopia is not a reality today.

In the real world, it is not unusual to find a complex design flow in operation, with best-in-class design and simulation tools being used to complement best-in-class enterprise PCB design flows. Unfortunately, the design and simulation tools are not usually integrated into the enterprise PCB flow and this can lead to inefficiency and, perhaps more importantly, errors creeping into a design.

For several reasons this is particularly true when RF/microwave content is to be incorporated into larger PCB designs.

The home-base environment for many RF/microwave designers is a specialist RF/microwave design tool, not an enterprise PCB flow tool. Consequently, at some point in the cycle a design created and simulated in an RF/microwave design tool will have to be re-created in the enterprise PCB flow tool. A number of different methods may be used to achieve this goal and, as is often the case, trade-offs must be made between the speed, ease and accuracy of the design transfer between platforms. Refer to Figure 1 to see the PCB design flow options.

FIGURE 1. The PCB design flow.

|

At one end of the spectrum, the design may be manually re-entered, component-by-component. While this is generally straightforward, it is very time-consuming and labor-intensive. Furthermore, there is a high risk of errors being introduced. At the other end of the spectrum are automated translations of schematic and/or layout designs. One of the more established methods of passing design information between design frameworks is to use the so-called intermediate file format (IFF) translation. IFF provides the possibility of bi-directional schematic and layout translation between design frameworks. While this greatly simplifies the process of migrating designs from one design framework to another, it comes at a price.

Before an IFF translation can occur, both design frameworks must contain compatible component libraries. This, of course, is not always the case. Consequently, an up-front investment is required to make the libraries compatible, and subsequent on-going maintenance is needed to keep the libraries synchronized.

A compromise option is to take the RF/microwave layout details into the enterprise PCB tool using any one of a number of industry standard formats such as Gerber or GDSII (Calma). However, even if the RF/microwave design is re-created perfectly in the enterprise PCB tool, there is still a possibility that unforeseen problems will be introduced, due to layout parasitics, when it is integrated onto the PCB layout together with other analog/digital circuits.

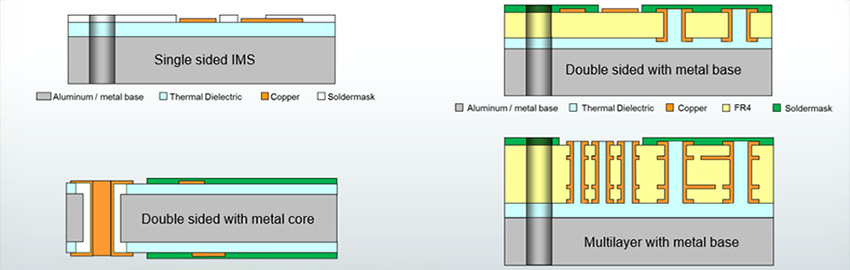

To understand why layout parasitics can cause such problems, it is necessary to know a little about the nature of RF/microwave signals and the design techniques used by RF/microwave designers. The first and most important factor is that RF/microwave circuit designers will often use a combination of discrete and distributed elements as components in a design. This immediately causes confusion, because a distributed element is essentially just a piece of metal printed onto the circuit board and is not considered a component; it would not appear on a bill of materials. An example of a distributed component is a microstrip transmission line, which may be used to distribute RF/microwave signals around the PCB. A microstrip line has an inductance that is associated with the current flowing along the line and capacitance due to the line being separated from ground by the dielectric substrate. The resulting classic L-C model accounts for the term distributed. In a multilayer PCB these distributed elements are implemented either as stripline or microstrip structures on the circuit board. The key electrical properties of these structures such as characteristic impedance and electrical length are determined by the physical width and length of the line, together with the thickness and dielectric permittivity of the substrate material.

During the RF/microwave circuit design process the distributed components are carefully specified and, for the purpose of simulation, are typically modeled using closed-form analytical models. Alternatively, electromagnetic (EM) simulation may be used to create more detailed S-parameter models. Clearly, it is important that the correct dimensions are assigned to the distributed components when the physical layout is created. This is an obvious area where errors may be introduced if a manual design re-entry method is used to integrate the RF/microwave design into the enterprise PCB tools.

Of course RF/microwave signals are electromagnetic (EM) in nature. Consequently, a microstrip transmission line is surrounded by an electromagnetic field. In the case of a microstrip transmission line, the EM field exists both in the air above and the dielectric substrate below the microstrip line. In certain circumstances the field coupling between adjacent microstrip lines may be a desired, intentional phenomena which can be used to good effect in particular designs such as edge coupled microstrip filters. However unwanted coupling between microstrip lines and the surrounding circuitry occasionally can cause unexpected problems. This unwanted coupling is another source of problems often introduced when the RF/microwave design is integrated together with other circuit blocks (analog/digital). In the past, to avoid unwanted coupling, crude rules of thumb have often been used to define no-go areas around microstrip/stripline transmission lines. However, this is no longer practical for today's complex mixed-signal, multilayer PCBs.

A process exists that can help identify both errors introduced by transferring design data between tools or due to unexpected proximity coupling effects. The method utilizes electromagnetic simulation techniques to accurately predict unwanted coupling in a PCB design and to verify that the RF/microwave layout is suitable. The starting point for this exercise is a completed PCB design, which is made available from an enterprise PCB tool source.

For this process, the Agilent EEsof's ADS and Momentum EM simulator are used to extract the layout parasitics. Circuit/EM co-simulation is used to verify the performance of the populated PCB.

FIGURE 2. Steps for creating the virtual PCB.

|

The basic steps to create the virtual PCB are outlined in Figure 2. It starts with the export of the PCB layout from the enterprise PCB design tool. A Gerber file format is used because it is widely supported in most EDA tools. Until recently, Gerber data was not an ideal starting point for layout generation if EM simulation was to be performed. This is simply because Gerber is intended to drive a photoplotter and for this reason produces many layout artifacts which need to be cleaned up prior to EM-simulation. Figure 3a illustrates this. It shows a typical Gerber layout (centerlines view) consisting of many overlapping strokes and flashes. The centerlines indicate the path taken by the photoplotter's light source to expose the high-contrast film. To overcome this problem, the GBRUnion tool was used to import the Gerber file into the layout. GBRUnion also simplifies the data by performing a union operation that adds contours to the layout geometry (Figure 3b), which in turn simplifies the mesh created by the simulator.

FIGURE 3a. Typical Gerber layout, center lines view ...

|

FIGURE 3b. ... and contours add to the Gerber files translated into layout.

|

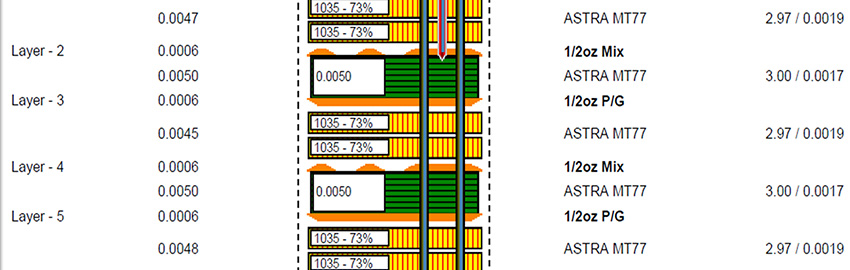

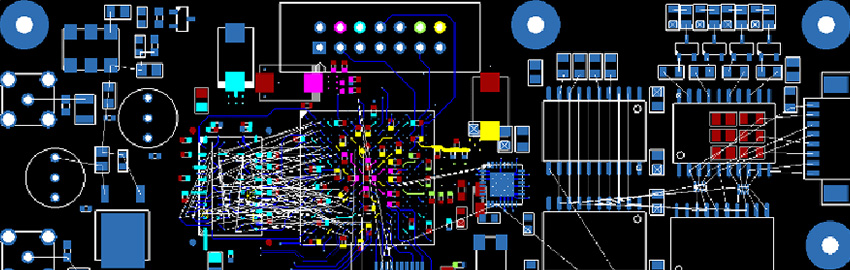

Figure 4 shows the imported PCB layout detail. The PCB is a relatively simple FR-5 board. It is 1.55 mm thick and has metalization on both the top and bottom faces of the board. Via hole connections through the board also are used. Before the EM simulation can be run on the imported layout, some additional setup is necessary:

FIGURE 4. The PCB layout imported into layout.

|

- Defining the substrate (dielectric layers: thickness, permittivity, dielectric loss tangent).

- Mapping the layout layers into the substrate definition.

- Adding ports to the layout.

In this case, as well as adding ports at the signal RF input and RF output locations, additional ports are also added at all locations where discrete components will be soldered to the board when it is assembled (Figure 5). This enables discrete components to be co-simulated together with the EM extracted layout parasitics. Depending on the size and complexity of the PCB and the amount of computer memory available, it may be necessary or judicious to reduce the PCB layout before running the EM simulation.

FIGURE 5. Simulator ports added to the PCB layout.

|

In this particular example, the layout was simplified by removing some of the non-RF signal traces. Any non-RF traces running close to the RF signal traces were left in so that coupling effects would be taken into account. The simulation was run to characterize the layout over a frequency range of DC to 5 GHz. This required just over 20 minutes of simulation time on a modest specification PC (1.6 GB processor). The output from the simulation is an S-parameter file—in this case, a 47-port S-parameter file. The S-parameter data can be readily used in any frequency domain circuit simulation tool. In this case, the ADS S-parameter simulator was used.

Following the EM simulation, the resulting model can be implemented as a layout look-alike component in the ADS environment. This greatly simplifies creating the schematic design (Figure 6). Initial simulations were run on the design to characterize the RF signal path from the RF input connector on the edge of the PCB to the RF input pad for the RFIC package. Short circuit links were used to close gaps left in traces intended for discrete components (DC blocking capacitors, and so on).

FIGURE 6. Schematic test bench, showing an EM-based layout look-alike component model.

|

This simulation of the bare board highlighted a resonance within the design band at approx 1.72 GHz (Figure 7a). The next step was to populate the PCB by adding all of the discrete components used in the real-world design (Figure 7b).

FIGURE 7a. Unexpected resonance simulated on the bare board.

|

FIGURE 7b. Schematic test bench showing an EM-based layout look-alike component model, populated with discrete components.

|

Simulation of the populated PCB revealed a second resonance at approx. 1.94 GHz. (

Figure 8). At this point, further simulations were performed to debug the problems in much the same way the problem would be de-bugged in hardware. Useful simulation tools like real-time tuning enable discrete component values to be adjusted and their effects observed, or discrete components can be removed from the virtual PCB. Using this approach it was determined that the 1.94 GHz resonance was being caused by the DC bias feed network, and closer inspection of the layout revealed that a misplaced via hole was connecting the RF signal path through the PCB to an isolated metal pad which was resonant at around 1.72 GHz.

FIGURE 8. Additional unexpected resonance simulated on the populated board.

|

FIGURE 9. Circuit response after fixing the resonance problems.

|

Armed with this information, a second virtual iteration of the PCB layout was produced, and the verification process was repeated to confirm the problems had been resolved (Figure 9). The verification process described here can be used to help identify and debug problems on new PCB designs with some RF/microwave content. And the process is not restricted to RF/microwave PCBs. A similar process could also be used to investigate signal integrity issues in high-speed digital board design applications. PCD&M

David Morris is a technical sales consultant at Agilent EEsof. He spent eight years as a microwave circuit/subsystem designer and has served four years in a product marketing/sales role. He can be reached at This email address is being protected from spambots. You need JavaScript enabled to view it..

REFERENCES

T.C. Edwards, "Foundations for Microstrip Circuit Design," Wiley, New York, 1981.

L.G. Maloratsky, "Reviewing the basics of Microstrip Lines,"

Microwaves & RF, March 2000.

S. DiBartolomeo, "Application Note: Importing Gerber into ADS Momentum using GBRUnion," Artwork Conversion Software Inc.