The use of blind microvias - and multiples of vias - can help reduce the discharge time of sheet capacitors.

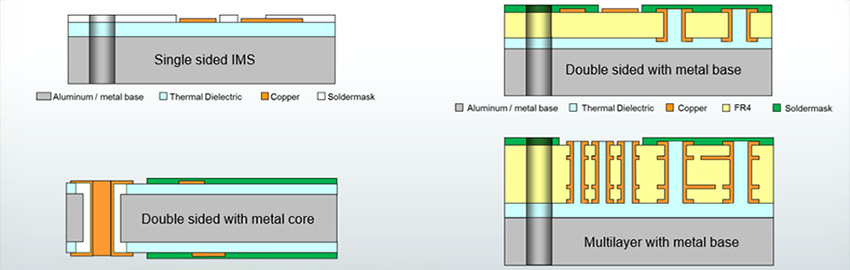

Buried sheet capacitance has been used for some time in sophisticated PCB designs. The ZBC 2000, whose patent is owned by Sanmina Corp., is a familiar example. Conceptually, this product consists of one or more inner layers with a .002" FR-4 core. Each such inner layer forms a sheet capacitor of approximately 500 pf per inch2. The original purpose of the technology was to replace the surface bypass capacitors with an internal alternative and thereby provide additional outer layer real estate for routing and active components. Later it was also found that a properly designed buried sheet capacitor is an effective method for containing EMI radiation.

This article is adapted from a paper presented by the author at IPC Expo in February 2006. It will analytically investigate the dynamic properties of buried capacitors when incorporated into a PCB. Techniques for improving the performance will also be examined.

Until now most similar studies focusing on the performance of buried capacitance have been empirical, relying upon measured responses. This paper will analytically investigate the dynamic properties of a buried sheet capacitor using an LCR lumped system analogy. The discussion considers various interconnect strategies and compares them to the discharge properties of an isolated sheet capacitor. Of special interest is the role played by the via interconnecting the sheet capacitor to the board.

The Sheet Capacitor

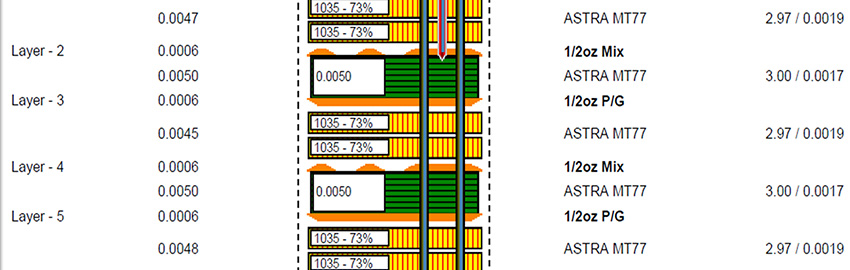

The typical sheet capacitor is a .002" inner layer core with copper sheets on each side (Figure 1). Unfortunately, the inclusion of a sheet capacitor into a MLB structure complicates the issue. In this case the current flows from the sheet capacitor through a via and to the device as shown in Figure 2.

FIGURE 1. A typical sheet capacitor structure.

|

FIGURE 2. A multilayer PCB with a sheet capacitor.

|

The result of interconnecting the sheet capacitor by a via to the Vcc pin of the device is to increase the time required for the capacitor to fully discharge. The issue is caused by the inductance associated with the via. The analysis presented here analytically quantifies the issue. The lumped system for a sheet capacitor in series with a via is shown in Figure 3.

FIGURE 3. Diagram showing a lumped system for a sheet capacitor in series with a via.

|

After the switch is closed, the capacitor discharges according to the governing equation:

(Eq. 1)

|

For purposes of this analysis it will be assumed that the inductance, resistance and capacitance are constant. The closed-form solution to this differential equation is:

Q = Ge-pt cos (qt-H)

(Eq. 2)

where

|

may be considered the reciprocal of the time constant and

may be considered the frequency of the current.

H and G are constants of integration. The boundary conditions are:

where Ve is the voltage associated with the sheet capacitor.

It follows:

|

H = tan-1 (p/q)

|

The following analysis will focus upon the behavior of the amplitude envelope in Equation 2. That is: e-pt which governs the flow of the charge Q stemming from the sheet capacitor. Notice that the time constant (τ=1/p) is a function of the inductance and resistance only, and independent of the capacitance of the sheet capacitor. Consequently, the discharge rate of the sheet capacitor will be a very weak function of the sheet capacitor material, since the resistance and inductance of the sheet capacitor will be shown to be small compared to the same properties of the via.

Typical Interconnection Structure Values

For the via. The resistance of the via with .001" thick copper is 679 micro-ohms per square, and it follows for a .013" via in a .062" board the resistance is

The inductance of a via can be approximated as:

(see Reference 2) where h is the length of the via and d the diameter in inches. For the case at hand,

Notice that the inductance is primarily a function of the length of the via and a weak function of the diameter. The capacitance of the via is:

| Cv = 1.41 εhd / tc pF (see Reference 2)

|

where ε is the dielectric constant and tc is the thickness of the via copper in inches.

which is minor compared to the sheet capacitor.

For the sheet capacitor. The capacitance of the sheet capacitor is assigned to be 500 pF. The inductance of the sheet capacitor is

| Lsc = 12.56 x 102 (h/w2) nH/m2 (see Reference 3)

|

where h is the distance from copper center to copper center (meters) and w is the effective width of the ground plane in meters. The inductance of the sheet capacitor is then

which is small compared to the inductance of the via. The resistance of the sheet capacitor is 679 micro-ohms per square per .001" of copper.

The lumped resistance, capacitance and inductance for the interconnected sheet capacitor are then

R = 1.88 x 10-3 ohms

L = 1.3 n Henrys

C = 500 pF

|

Analysis

First we will develop the numerical values for the constants in Equation 2.

or

is approximately one microsecond.

q = 1.5 x 109 / sec or 200 MHz

H = 10-3

|

which is small and the cos H is approximately 1.0. Consequently,

G = CVe

and

Q= CVe exp (-.75x106t) cos (1.5x109t)

(Eq. 3)

|

define Q0 = CVe the initial charge. Then

(Eq. 4)

|

Our focus will be on the exponential envelope, i.e.,

(Eq. 5)

|

The decay in the charge is shown in Figure 4.

FIGURE 4. Chart showing amplitude decay time in microseconds.

|

As seen, 90% of the original charge has been released after the approximately three microseconds. Most of the delay is caused by the via. In theory, the absolute minimum time required to discharge the sheet capacitor would be through a via with no impedance. Using this metric, one can then judge the penalty associated with the interconnection system.

The form of the governing equation in this case is still Equation 5. The time constant for the sheet capacitor alone is

(Eq. 6)

|

The dynamics of the discharging sheet capacitor can be examined by focusing upon the exponential envelopes shown in Figure 5.

FIGURE 5. Chart showing the different decay times for discharge through a via vs. through a sheet capacitor only.

|

As already noted, about three microseconds are required to discharge the capacitor through a via. On the other hand, with a zero impedance via, the time would be about a quarter of a microsecond. Obviously, because of the associated inductance, the via greatly reduces the discharge rate.

We have now bracketed the performance range of the sheet capacitor. Our interest now concerns the influence of other interconnect strategies on this phenomena.

Some improvement can be obtained by using blind microvias. For this analysis, assume the via to be .004" long and .005" in diameter. Using the equation above for vias the inductance is

Lvia = 0.05 nH (as compared to over 1.0 nH for a conventional via)

|

The resistance is

The time parameter p in Equation 7 is then

|

L = 0.16 nH

R = 0.82 x 10-3 ohms

and

p = 2.6 x 106 per sec or π = 380 ns

(Eq. 7)

|

which is about half of the conventional via. The discharge rates are compared in Figure 6.

FIGURE 6. Chart showing the different decay times for discharge through a via, a microvia and a sheet capacitor only.

|

While the discharge time for the microvia is more than the sheet capacity, it is a factor of three less than the conventional via.

It should also be pointed out that by using a blind microvia which as observed reduces the inductance; the noise generated when charge is drawn from the sheet capacitor will in turn be reduced since the noise is proportional to

Next, we will consider the case of discharging through two identical conventional vias. The lumped system is shown in Figure 7.

FIGURE 7. An example of a lumped system.

|

The governing equation in this case is:

(Eq. 8)

|

Using the values already stated above for Lv, Rv and Rsc

The amplitude decay is shown in Figure 8 and compared to the other scenarios discussed earlier.

FIGURE 8. Chart showing the different decay times for discharge through a via, a microvia and a sheet capacitor only, and two matched vias.

|

As seen, using multiple vias improves reduces the decay time as compared to a single via, but not to the extent of a microvia. PCD&M

Dr. J. Lee Parker is an independent consultant with his company JLP Consultants. He has a Ph.D. in aeronautical engineering and holds nine patents. He can be reached at This email address is being protected from spambots. You need JavaScript enabled to view it..

REFERENCES

1. HADDCO Buried Capacitance Manual

2. Johnson and Graham, "High Speed Digital Circuits," Prentice Hall, 1993

3. University of Missouri-Rolla Electromagnetic Compatibility Laboratory