When I first started in electronics back in 1991, through-hole was still dominant and SMT was just taking hold. It wasn’t long after, however, when we began hearing about multichip modules, or MCMs. Conferences sprung up, publishers dedicated entire issues to the subject, and trade groups started writing standards.

And then … not much. MCMs never became the dominant packaging style some analysts predicted.

But will they?

When the Semiconductor Industry Association ceased its roadmapping activities, a host of organizations, including IEEE, SEMI, ASME and others, jumped in. Last month, they launched the second edition of the Heterogeneous Integration Roadmap. Heterogeneous integration refers to the integration of separately manufactured components into a higher-level assembly (SiP) that, in the aggregate, provides enhanced functionality and improved operating characteristics.

Or, as Dick Otte and Phil Marcoux wrote in this magazine in August (“Interconnects Drive Heterogenous Assembly and Substrate Options”), “heterogenous is the latest branding effort to promote the assembly of dissimilar electronic components. In the past these could be called multichip modules [itals mine], 2.5-D, 3-D and – really going back – ‘hybrid’ assemblies.”

Multichip modules.

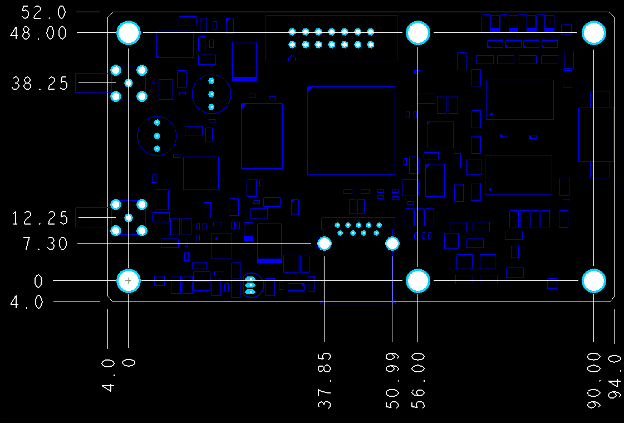

For the uninitiated, an MCM consists of multiple ICs or dies integrated on a common substrate. The resulting module is treated for processing purposes as a single component.

The HIR is called a roadmap to the future of electronics, identifying technology requirements and potential solutions. The sponsoring organizations wanted to spur “pre-competitive collaboration” among industry, academia and government, in the hopes of speeding up progress. Not surprisingly, IEEE has promoted the use of heterogeneous assembly at its popular ECTC conference. PCB designers have traditionally eschewed die-level issues in favor of focusing on the package-to-board interconnection. Is there reason to think that might change?

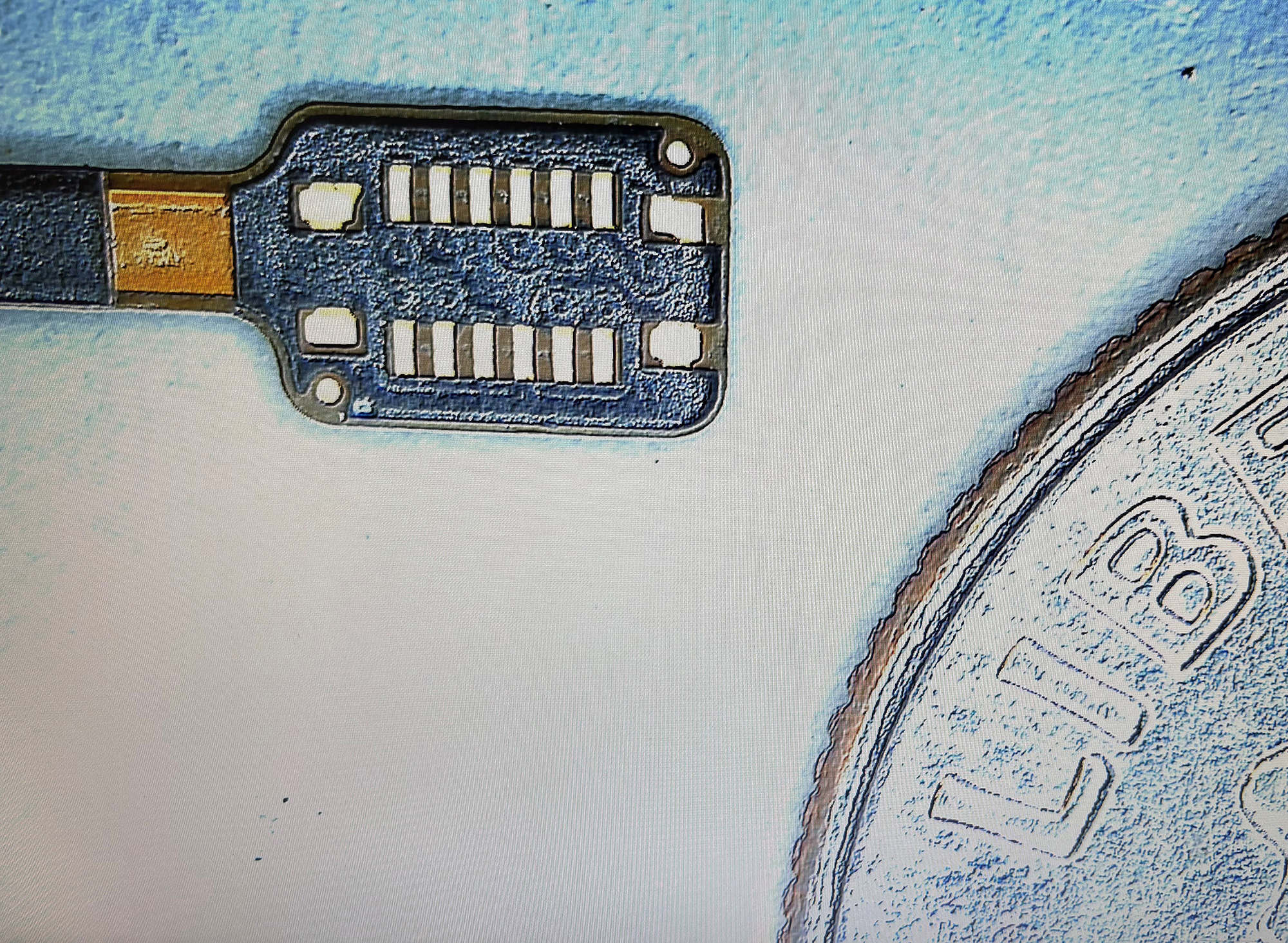

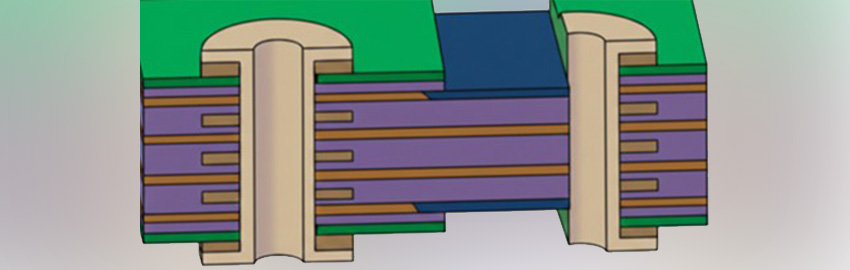

At ECTC and in the HIR, the term chiplets has emerged as a technology in waiting. And, points outs Jan Vardaman, our resident components packaging editor, chiplets are MCMs. The substrate for chiplets could be a wafer or an organic package. The die might be wire-bonded, but solder ball interconnect (aka flip chip) is more common, and hybrid bonding is emerging.

Work is ongoing in many centers. Besides some of the largest foundries, academia is taking a look. Teams of researchers at UCLA, led by Dr. Puneet Gupta and Dr. Subramanian Iyer, have developed a silicon-to-silicon concept that uses nanoscale wires to directly connect bare chips right on the wafer. They claim their idea, which they call silicon-interconnect fabric, permits a far greater number of chip-to-chip connections capable of transmitting data at faster speeds, at lower power, and without all the excess heat. (Dr. Gupta explained the process on our PCB Chat podcast in October.) The twist here is use of copper pillars for solder attachment or thermo-compression bonding.

That designers could save on power and possibly depress heat should open some eyes. Chip and hardware designers have long been grappling with how to manage the heat inside these packages. What’s far hairier is the notion the work of placing and soldering parts might not just become a die-level phenomenon, but it could be moved entirely upstream, eliminating the need for component assembly.

For that I turned back to Marcoux. He points out this is actually at least the third time MCMs have popped up as the technology of the future. And he allows chiplets are “attractive” from the IC perspective because it’s “not optimum to fabricate all circuit functions on the same wafer using the same processes.” For example, says Marcoux, “voltage regulators require different diffusions and oxide thicknesses than RAMs, etc. Analog functions are more optimum with bipolar compatible fab processes than digital processes.”

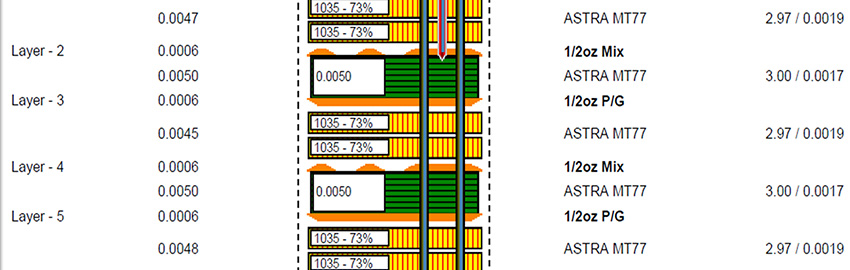

According to Marcoux, three hurdles may conspire to prevent silicon as a chiplet array substrate from taking hold: 1) The cost of silicon far exceeds that of PCB materials; 2) adding more than two layers causes adhesion problems and thus yield issues, which can mean wider traces to promote adhesion, and wafer planarization and metal deposition pumping processes that truly inflate costs; and 3) interconnecting the wafer externally is complex and, in his words, “not cheap.”

In the ongoing battle of silicon vs. package, the package always seems to win. PCB designers and contract assemblers can breathe easy.